Nios II 處理器是 Altera(現 Intel PSG)提供的一種可配置的軟核處理器,廣泛應用于 FPGA 嵌入式系統設計中。其強大的靈活性和可定制性,使得外圍設備(Peripheral)的設計與集成成為開發中的關鍵環節。本文將系統性地介紹 Nios II 外圍設備的核心概念、設計流程,并重點推薦相關的講義文檔與學習資源,特別是 CSDN 平臺上的優質下載資源,旨在為開發者提供一條清晰的學習與實踐路徑。

一、Nios II 外圍設備概述

Nios II 處理器通過 Avalon 交換架構與外圍設備通信。外圍設備是擴展處理器功能、與外部世界交互的關鍵模塊,主要分為兩類:

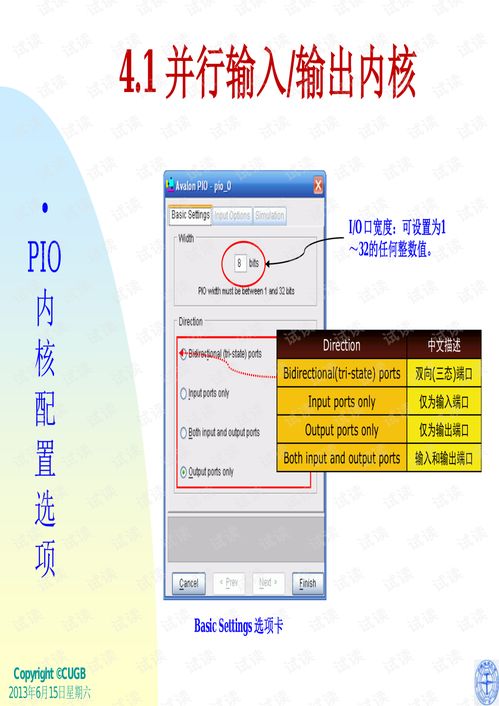

- 標準外圍設備:由 Intel 或第三方提供,如 UART、定時器、PIO、SPI、I2C、SDRAM 控制器等。這些設備經過高度優化和驗證,可直接通過 Qsys(現為 Platform Designer)工具集成,快速構建系統。

- 自定義外圍設備:開發者根據特定應用需求,使用硬件描述語言(如 Verilog 或 VHDL)自行設計。這提供了最大的靈活性,可以實現專用加速器、特殊接口等。

二、外圍設備的設計與集成流程

- 需求分析與規劃:明確系統所需的外設功能、性能指標及接口類型。

- 選擇與創建:對于標準外設,直接在 Platform Designer 中從 IP Catalog 添加;對于自定義外設,需先進行 RTL 設計,并封裝為 Avalon 兼容的 IP 核。

- 系統集成:在 Platform Designer 中,將 Nios II 處理器核、內存控制器、所選外設等通過 Avalon 互連架構連接起來,并配置地址映射、中斷等參數。

- 軟件驅動開發:在 Nios II Software Build Tools for Eclipse 中,基于 HAL(硬件抽象層)API 或直接操作寄存器,為外圍設備編寫驅動程序和應用軟件。

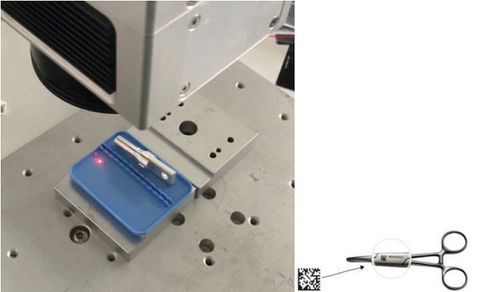

- 系統驗證與調試:將硬件配置(.sof)下載到 FPGA,運行軟件程序,利用 SignalTap II、System Console 等工具進行聯合調試。

三、關鍵學習資源:講義文檔與 CSDN 下載推薦

理論學習與文檔查閱是掌握 Nios II 外圍設備開發的基礎。以下是一些核心資源方向:

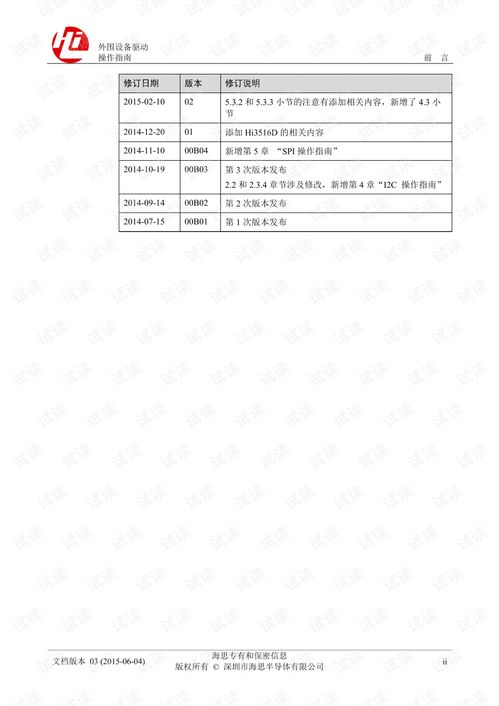

- 官方文檔:Intel 官網提供的《Nios II Processor Reference Handbook》、《Embedded Peripherals IP User Guide》是權威指南,詳細闡述了架構、IP核詳述及編程模型。

- 大學講義與實驗指導:許多高校的 FPGA 或嵌入式系統課程會發布詳細的講義。這些資料通常從入門開始,循序漸進,包含大量原理圖和代碼示例,非常適合初學者構建知識體系。

- CSDN 資源下載:CSDN 作為國內重要的開發者社區,積累了豐富的用戶上傳資料。搜索關鍵詞如 “Nios II 外圍設備 講義”、“Nios II 自定義外設”、“Qsys 教程” 等,常可找到以下寶貴資源:

- 中文翻譯或整理的官方手冊精華:降低了語言門檻,快速抓住重點。

- 完整的項目實踐文檔:包含從硬件設計到軟件編程的全過程,配有詳細注釋的代碼,極具參考價值。

- 特定外設的深度解析:如如何設計基于 Avalon-MM 或 Avalon-ST 接口的自定義 DMA 控制器、視頻處理流水線等。

- 常見問題集錦與調試技巧:匯聚了眾多開發者的實踐經驗,能幫助有效避坑。

下載建議:在 CSDN 下載時,注意查看資源的評分、評論和更新日期,優先選擇評價高、內容較新的文件。合理利用積分機制。

四、實踐建議與

掌握 Nios II 外圍設備,必須堅持“理論結合實踐”。

- 從標準外設入手:先用 Platform Designer 搭建一個包含 UART、PIO、定時器的簡單系統,并編寫程序控制 LED 閃爍和串口打印,熟悉完整流程。

- 挑戰自定義外設:從一個簡單的寄存器接口外設開始,例如一個 LED 控制器,逐步增加中斷、流模式等復雜功能。

- 深入研究參考設計:仔細分析官方和社區提供的優秀設計實例,理解其架構和代碼風格。

- 參與社區討論:在 CSDN 博客、論壇、Altera/Intel 官方社區等平臺提問與交流,往往能獲得意想不到的啟發。

Nios II 外圍設備開發是 FPGA 軟核應用的核心技能。通過系統學習官方文檔,善用 CSDN 等平臺上的優質講義和項目資源,并輔以循序漸進的動手實踐,開發者能夠高效地構建出功能強大、量身定制的嵌入式系統。